Can’t find your discipline or profession? Write to us and we’ll

do our best to work something out.

Every project is unique.

We adjust our services to your needs.

The Libera Digit 125 is designed to turn various raw detector signals into meaningful data and deliver it to user’s control system. The instruments provide a base from which to develop users own application by combining their domain knowledge with our expertise in instruments design.

General description:

All the building blocks – from the analog front-end, FPGA processing, supporting firmware and software infrastructure, as well as the high-level user interface adapters form a working template with the possibility to extend its functionalities – allowing users to focus only on the core part: the signal processing algorithms.

AC and DC-coupled versions provide input bandwidths that suit both time-domain processing and narrow-band or frequency domain applications. The instruments are network-attached devices, with standard interfaces that facilitate integration into the control system (EPICS, Tango, TCP-IP socket, HTTP etc.).

*If higher sampling rates and a more powerful platform is required, Libera Digit 500 is the preferred instrument.

Benefits:

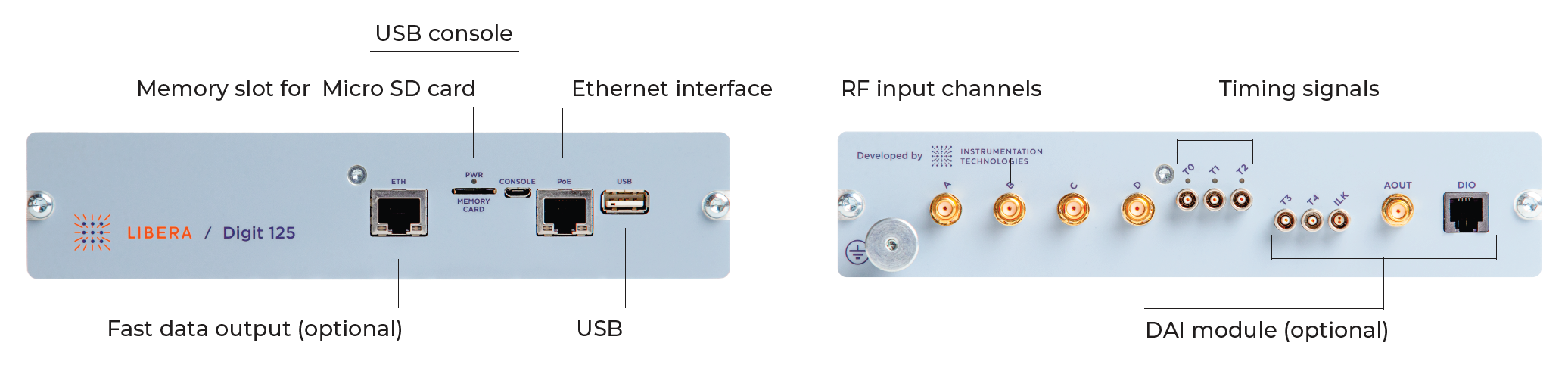

Libera Digit 125 front and back panel:

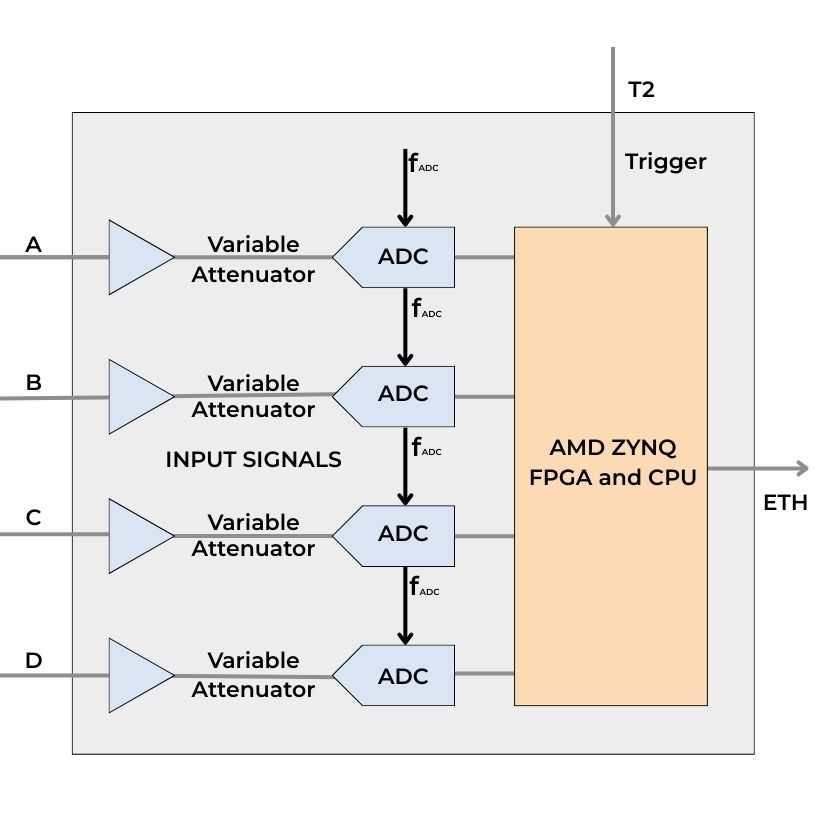

Data Processing:

In the analog front-end, input signals can be attenuated using SW-controlled variable attenuators with 0-31 dB attenuation. FPGA provides real-time averaging alghoritm. Post-mortem functionality is controlled by a special T1 trigger input. Configurable segmentation of the output buffers is designed to cover a range of different acquisition modes.

Libera Digit 125 block diagram:

| Variant | DC | AC |

| General product code | L1251.00D | L1251.00A |

| Channel number | 4 | 4 |

| Sampling frequency [MS/s] | 125 | 125 |

| Resolution [bit] | 14 | 14 |

| BW | DC-40 MHz | 10 MHz - 700 MHz |

| Coupling | 50 Ω/1 M Ω | 50 Ω |

| Max input | ±5 V @ 50 Ω 1.25 V @ 1M Ω | 1 V/10 dBm |

| Input again / attenuation | 0-31 dB | |

| Triggering level | 3.3 V TTL LEMO | 3.3 V TTL LEMO |

| Max trigger frequency [Hz] | 2 | 2 |

| Reference clock | Yes | Yes |

| FPGA | Xilinx Zynq 7020 | Xilinx Zynq 7020 |

| PoE | Yes | Yes |

| Access interfaces | SSH/Tango/Epics/HTTP/Telnet/Python/ Matlab/LabView | SSH/Tango/Epics/HTTP/Telnet/Python/ Matlab/LabView |

| Available extensions | - DAI1 module | - DAI1 module |

| Max acquisition length [samples] | 8 M | 8 M |

| Dimensions | H: 1 U, W: 9.5" (rack mountable with a kit), D: 210 mm | H: 1 U, W: 9.5" (rack mountable with a kit), D: 210 mm |

Libera Digit 125 is used at the following labs:

Can’t find your discipline or profession? Write to us and we’ll

do our best to work something out.

We adjust our services to your needs.