Can’t find your discipline or profession? Write to us and we’ll

do our best to work something out.

Every project is unique.

We adjust our services to your needs.

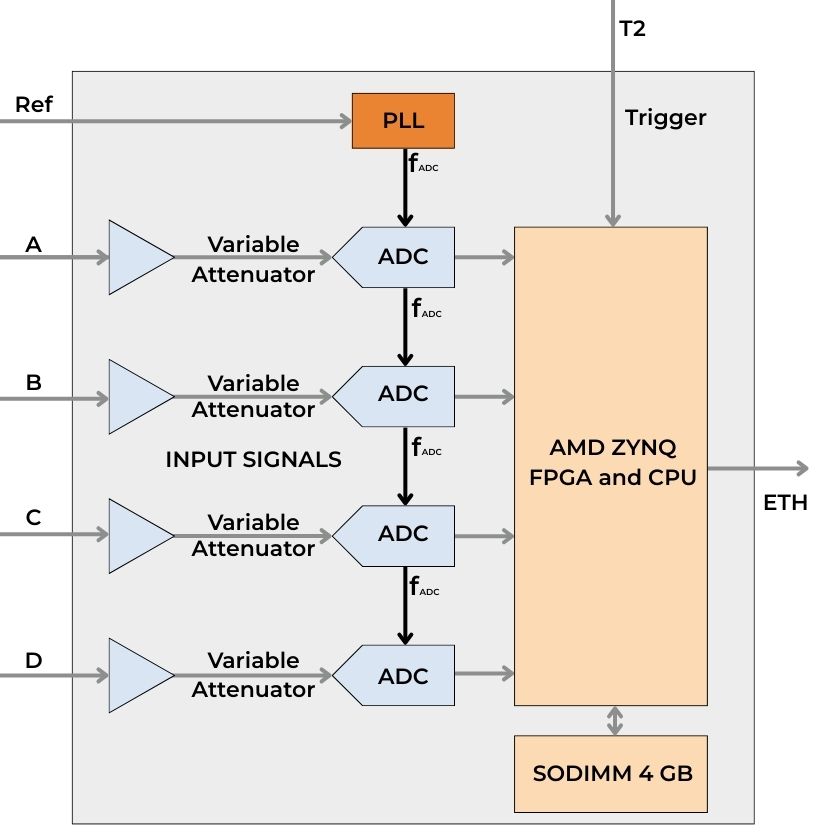

The Libera Digit 500 is a state-of-the-art beam current monitor readout and processing unit that supports three main applications:

In parallel, with a 500 MHz sampling rate, RF reference locking, low noise and wide dynamic range, it also serves as a powerful starting platform for a general-purpose 4-channel digitzer to which various tailored solutions can be added or functionalities extended. This way, users domain knowledge is combined with our expertise of high-performance instrument design and turning raw signals into meaninful data.

Benefits:

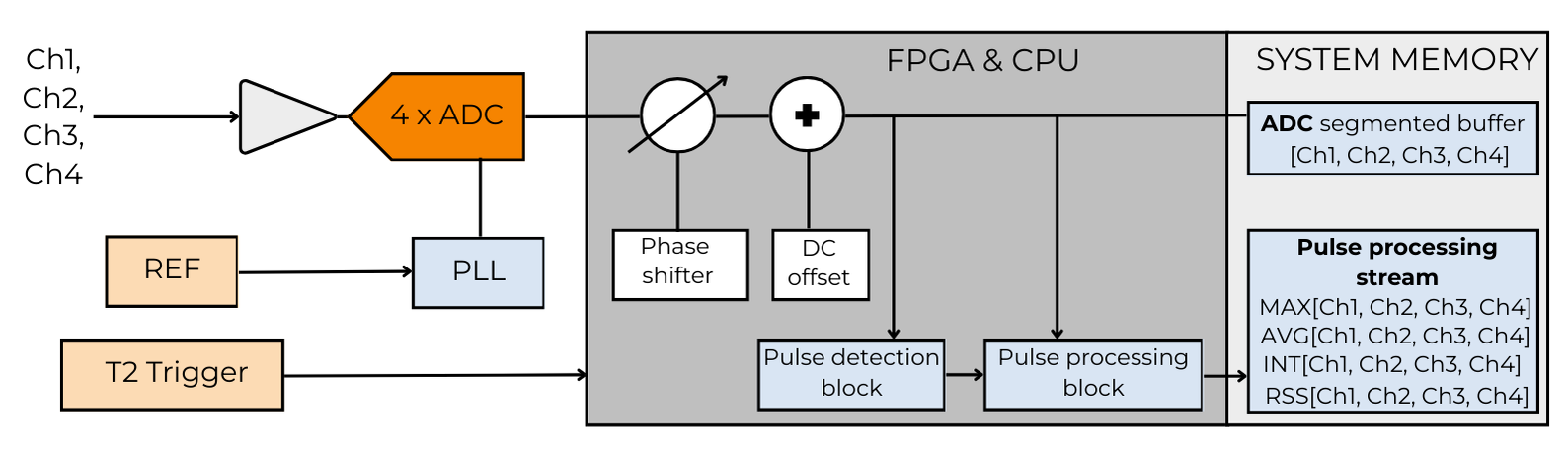

Data Processing:

There are three main beam current monitoring applications:

Pulse auto-detection and characterization

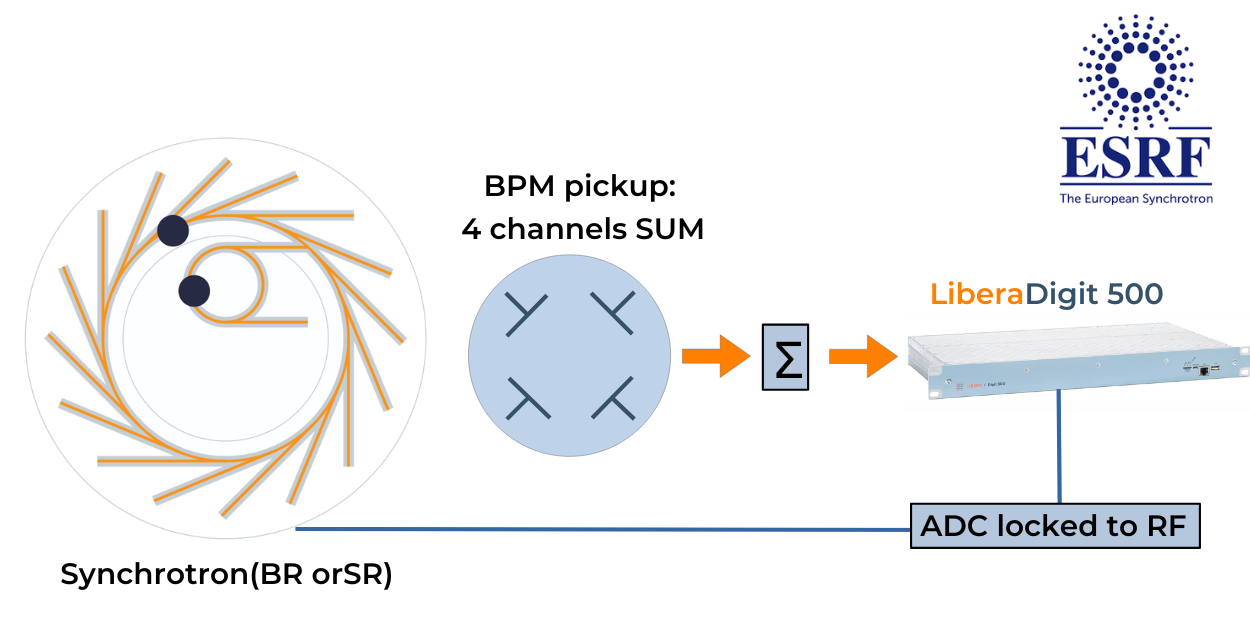

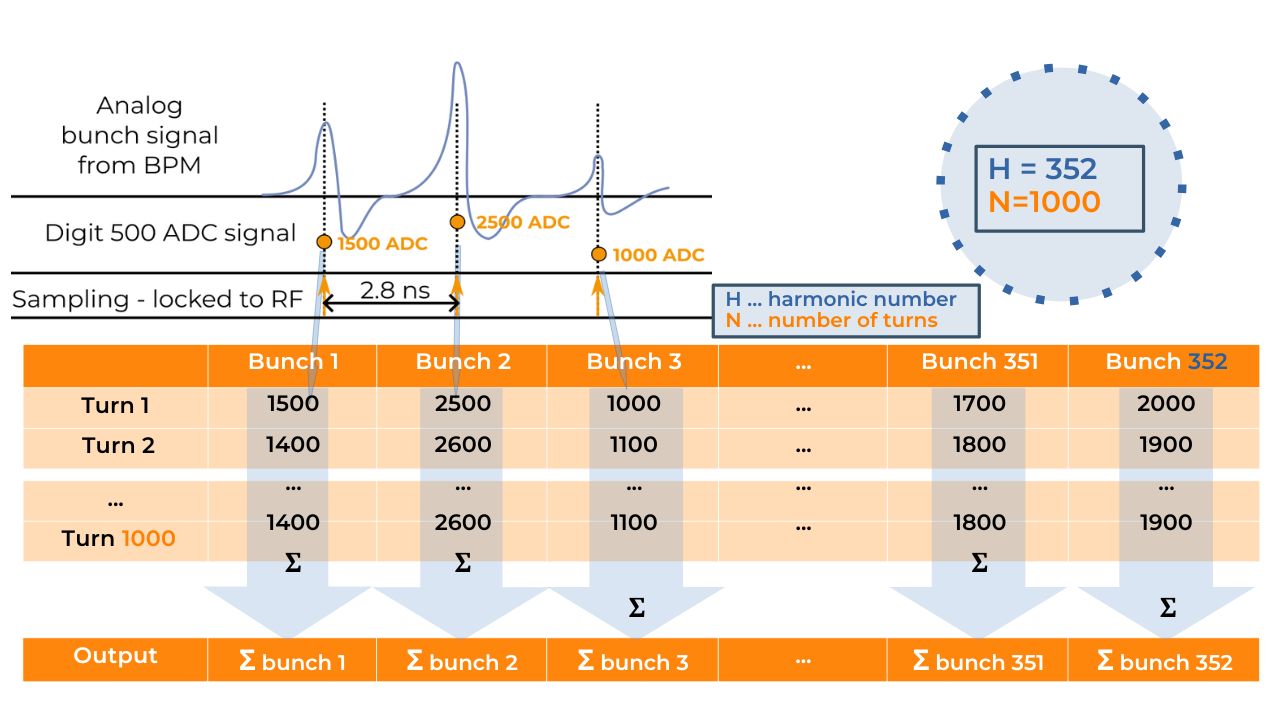

Fill pattern monitors:

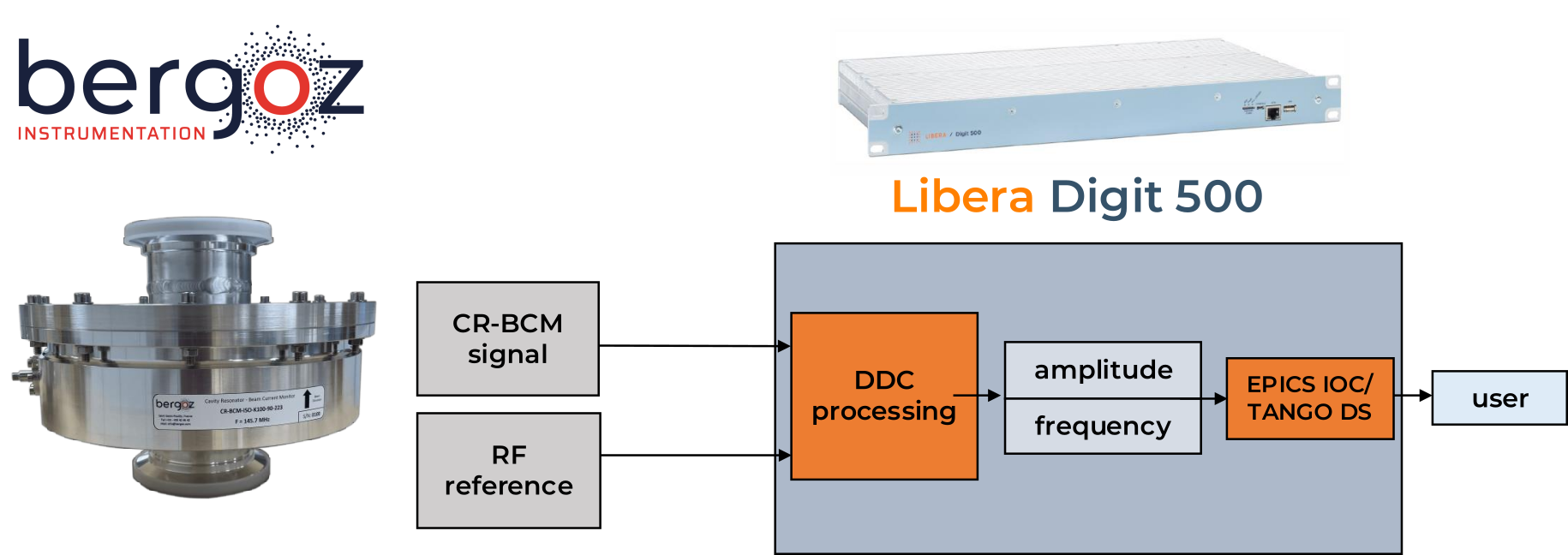

Resonant cavity beam current monitor:

High-performance general-purpose digitizer:

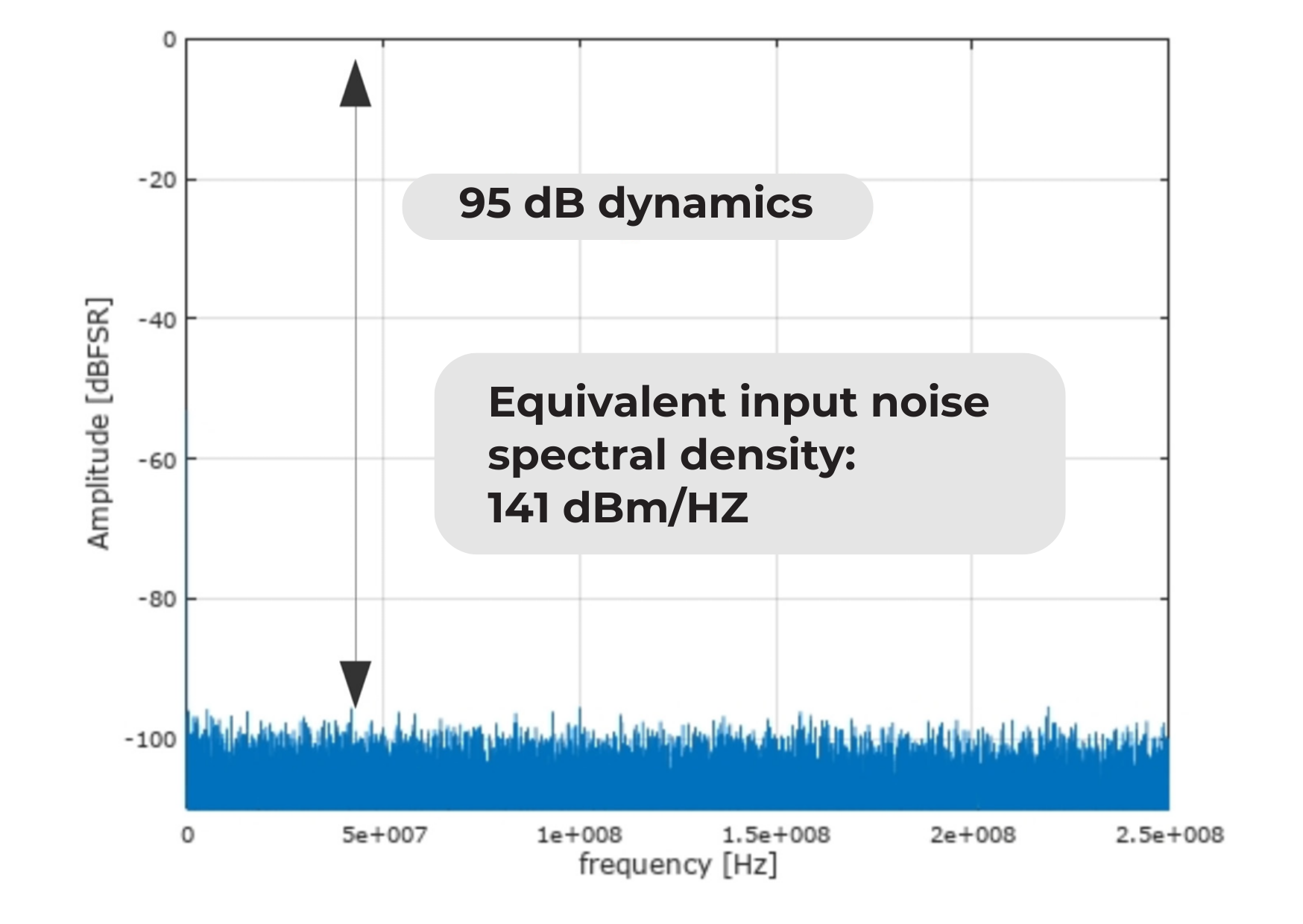

Performance:

The dynamic range of the system is over 90 dB.

| Variant | DC | AC |

| General product code | L5001.00D | L5001.00A |

| Channel number | 4 | 4 |

| Sampling frequency [MS/s] | 500 | 500 |

| Resolution [bit] | 14 | 14 |

| BW | DC-250 MHz | 1Mhz - 2 GHz |

| Coupling | 50 Ω | 50 Ω |

| Max input | 1 V/10 dBm | 1 V/10 dBm |

| Input again / attenuation | 0-31 dB | 0-31 dB |

| Triggering frequency [Hz] | 3.3 V TTL LEMO | 3.3 V TTL LEMO |

| Max trigger frequency [Hz] | 500 (can be extended up to 1000) | 500 (can be extended up to 1000) |

| Reference clock | Yes | Yes |

| FPGA | Xilinx Zynq 7035 | Xilinx Zynq 7035 |

| PoE | No | No |

| Access interfaces | SSH/Tango/Epics/HTTP /Telnet/Python/Matlab/LabView | SSH/Tango/Epics/HTTP /Telnet/Python/Matlab/LabView |

| Available extensions (SW to be developed by the user) | - DAI1 module - SFP connectors | - DAI1 module - SFP connectors |

| Max acquisition length [samples] | 500 M | 500 M |

| Dimensions | H: 2 U, W: 19" (rack mountable), D: 236 mm | H: 2 U, W: 19" (rack mountable), D: 236 mm |

| Pulse processing module: pulse area calculation, pulse width calculation, root square sum, and integral sum |

| SFP connectors: four optional small pluggable slots (SFP) which can be used for fast data |

| Digital phase shifters to fine-tune the phase differences between the input channels |

| Digital Downconverter module: allows extraction of the amplitude and frequency of a specific signal component |

| Bunch Charge Calculation module: allows the calculation of the bunch charge over several turns in electron synchrotrons |

Libera Digit 500 is used at the following labs:

Can’t find your discipline or profession? Write to us and we’ll

do our best to work something out.

We adjust our services to your needs.